BACKGROUND

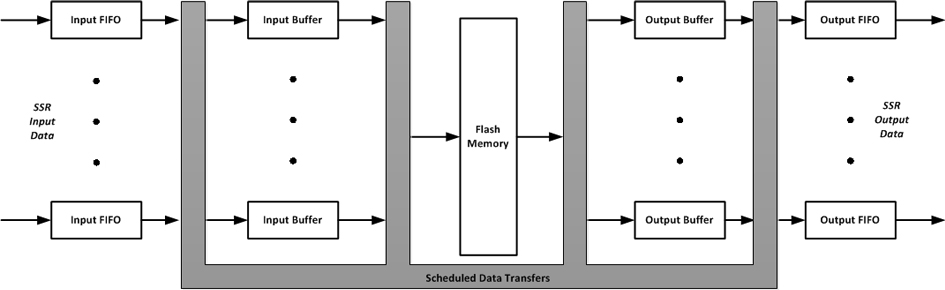

The sensors and communications systems of space missions now under development require unprecedented capabilities for data handling, storage, and communication by the spacecraft. In recent years, SwRI has gained substantial market share in the development of new solid-state recorders (SSRs) for space applications. SwRI’s patented design approach employs a hierarchical sequence of random-access memories and nonvolatile flash memories to provide flexible, high-performance data storage and playback. However, the performance objectives for next-generation SSRs depart from the capabilities of current designs by several orders of magnitude and new approaches are required to achieve the performance requirements of these applications. This research project developed capabilities for next-generation SSRs by developing a formal and rigorous mathematical model of data flow in SSRs and identifying new hardware architectures that overcome critical performance bottlenecks.

APPROACH

This research project focused on the mathematical analysis of data flow in an SSR and the development of new design and simulation tools to support next-generation, high-performance recorders. We explored data buffering architectures and identified new approaches that provide higher system throughput. We also formulated new mathematical upper bounds on buffer sizes and identified constraints on the operation of data queues to guarantee no loss of data. We developed a new heuristic approach for the automated scheduling of data transfers within the SSR and developed analysis methodologies for the shared buffers often used in these systems. In addition, we identified new electronic components, including field-programmable gate arrays, high-performance flash memories, and volatile memory technologies that are suitable for use in space applications and provide enhanced capabilities for SSR designs.

ACCOMPLISHMENTS

Results from this research program have provided technical approaches for high performance next-generation SSR applications. New software tools were developed that expanded SwRI’s SSR design and analysis capabilities. These include buffer transfer schedule design tools that meet data flow requirements while minimizing buffer sizes, new bounds used to prevent data loss by guaranteeing buffers do not overflow, and new techniques to validate data transfer schedules for buffers sharing common physical memory devices. We used the new techniques to redesign SSRs for existing applications, discovering design improvements that could be used for similar application in the future. We also utilized the new tools to formulate practical solutions for next-generation SSR designs achieving new levels of performance meeting key functional criteria in client inquiries.

Figure 1: Generalized SwRI SSR architecture illustrating coordinated data transfers between FIFOs, buffers, and flash memory.