Background

This project was undertaken to address the discontinuation of the heritage Charge Sensitive Preamplifier (CSP) previously used in space plasma instruments such as SWiPS and IES. With no available commercial replacement, the lack of a CSP with the required sensitivity and count-rate capability posed a risk to ongoing and proposed missions. The objective was therefore to develop, fabricate, and validate a flight-like CSP assembly compatible with the existing sensor stack. This new design aimed to replicate the electrical performance of the legacy solution while ensuring mechanical compatibility and maintaining robustness against crosstalk, electromagnetic interference (EMI), and digital interfacing challenges.

Approach

The project’s objective was to design and evaluate a replacement CSP assembly that met three critical criteria: (1) mechanical fit within the sensor stack, (2) equivalent or improved sensitivity and crosstalk performance, and (3) digital compatibility with FPGA-based discrimination systems. The methodology included:

Mechanical Integration: A vacuum-safe 3D-printed mock-up was fabricated to confirm board fit, connector clearance, and mounting tolerances.

Electrical Testing: Crosstalk and EMI were measured using controlled charge injection across multiple channels to assess noise coupling and interference mitigation.

Digital Compatibility: CSP outputs were interfaced with an FPGA running a threshold-based differentiator. This confirmed the ability to discriminate and count pulses at MHz rates.

Component Substitution: Two non-flight-qualified components were used for prototyping expediency; their footprints and characteristics match qualified counterparts, ensuring no redesign is required in transition.

Thermal Considerations: While full thermal testing could not be performed due to facility constraints, preliminary assessments leveraged historical data and partial bench results.

Accomplishments

Mechanical Verification: Successful integration of CSP boards into the 3D-printed sensor assembly mock-up with proper alignment and connector clearance.

Electrical Performance: Crosstalk and EMI measurements demonstrated compliance with benchmarks from earlier designs, confirming noise mitigation strategies were effective.

Digital Interfacing: FPGA-based tests showed reliable pulse discrimination and counting up to 5 MHz, with higher rates achievable using faster FPGA clocking.

Partial Flight Readiness: Prototype substitutions validated circuit performance while ensuring a smooth path to qualified flight components.

Metrics of Success: Three of five goals were met — sensitivity, crosstalk, and mechanical compatibility. Thermal testing and fully flight-qualified part testing remain open items for future work.

Because three goals were achieved, the project was considered a success.

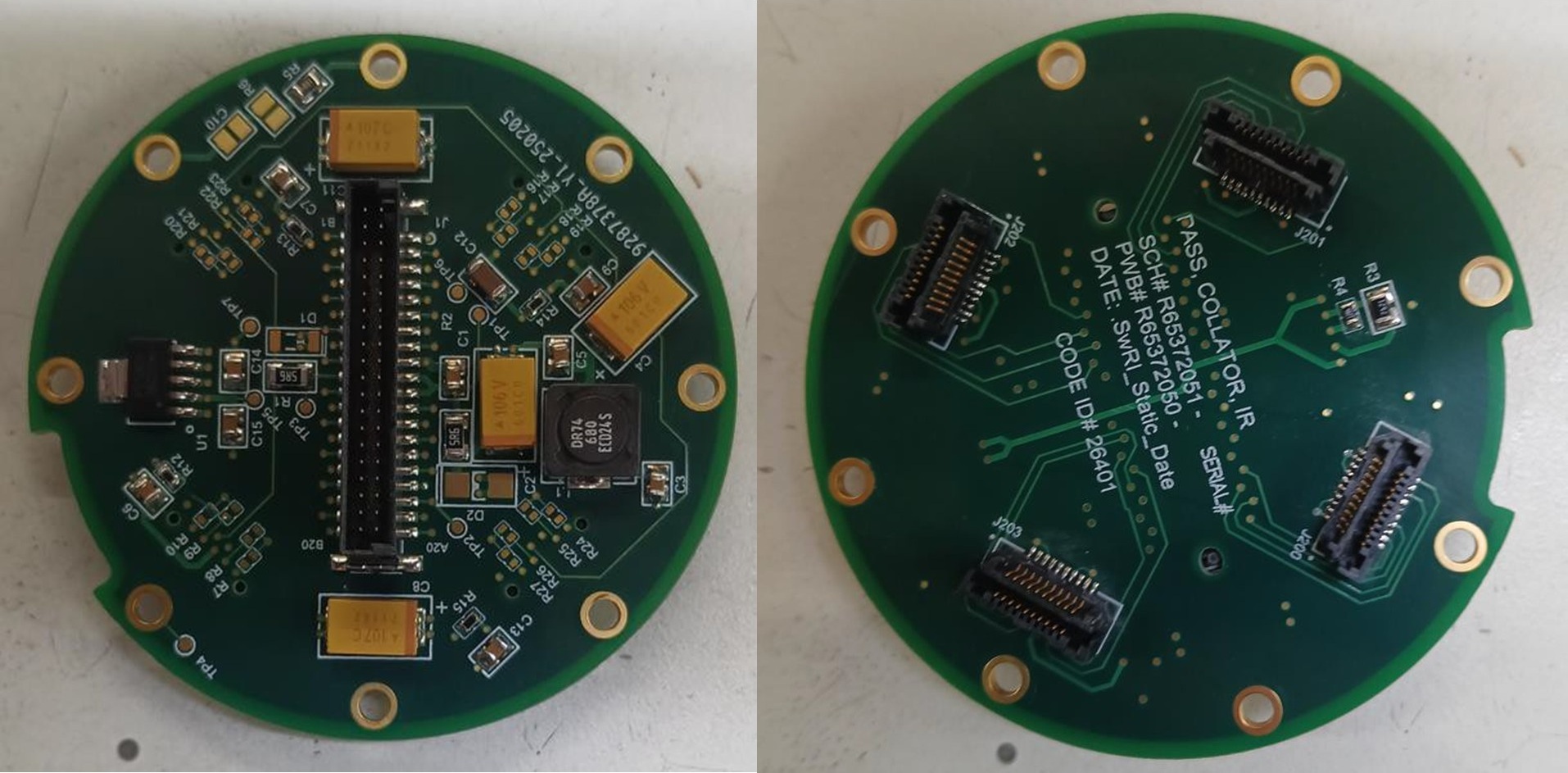

Figure 1: Collator board, top (left) and bottom (right) views.

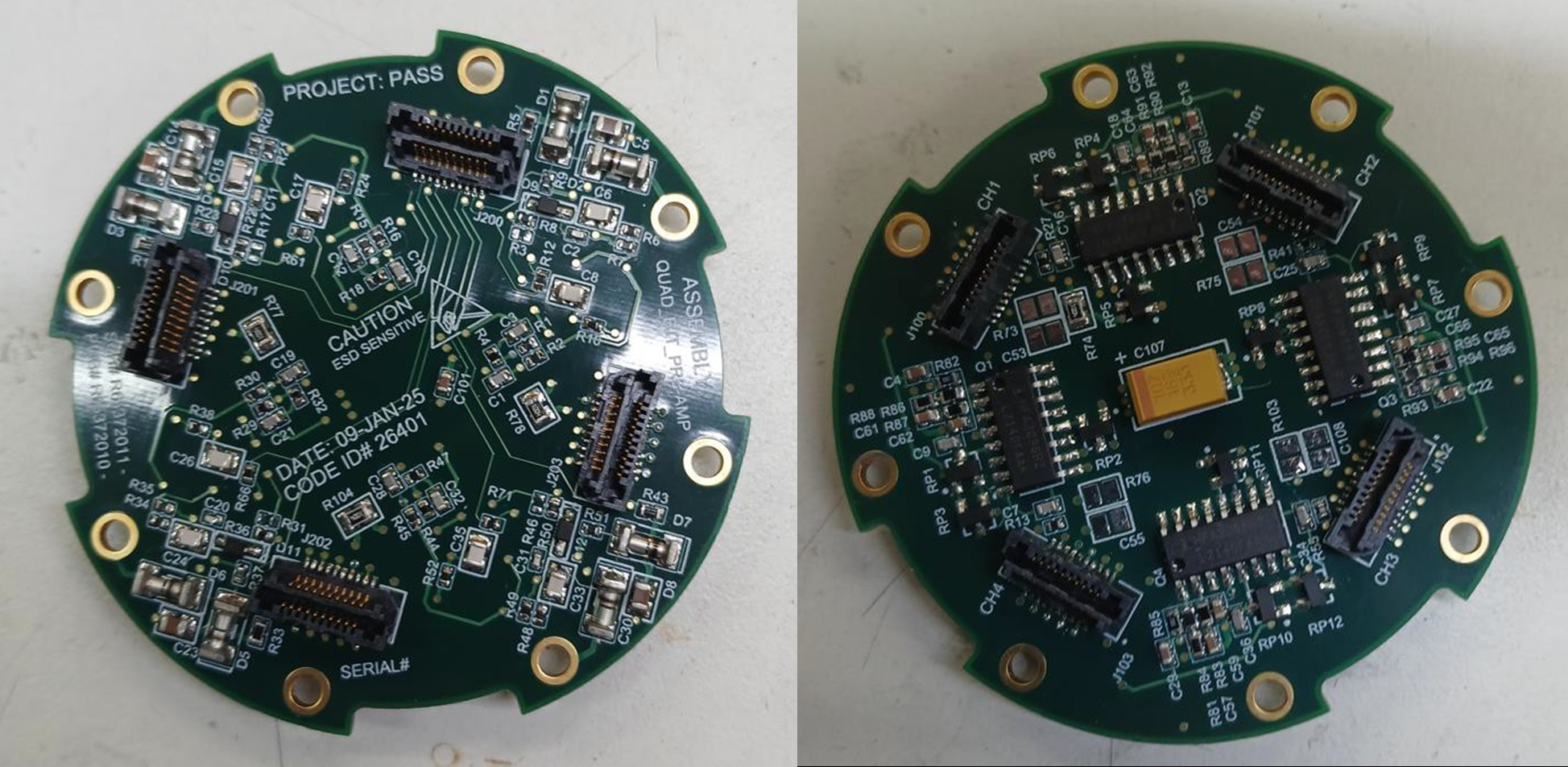

Figure 2: Pre-amplifier board, top (left) and bottom (right) views.